-

基本传输

一个beat(一笔)rw操作,分为addr phase and data phase; -

hready驱动总线周期的推进

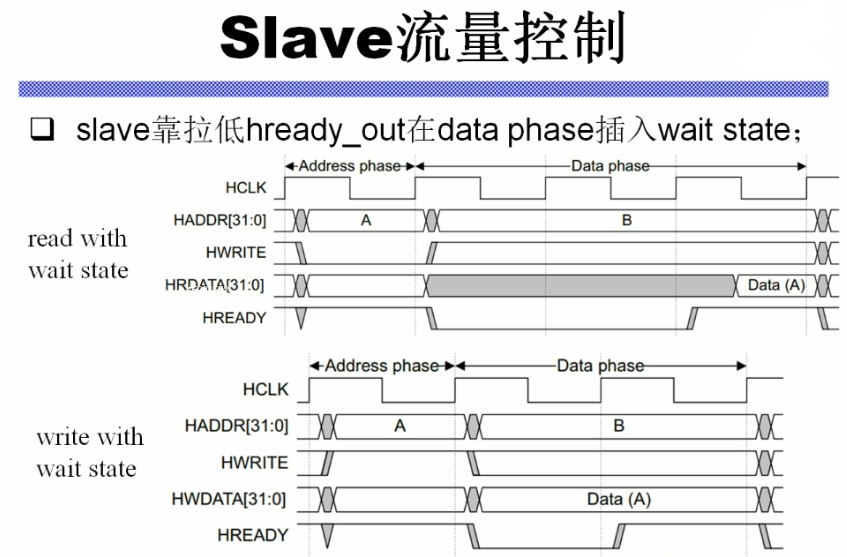

- AHB的流量控制

slave靠拉低hready_out在data phase插入wait state;

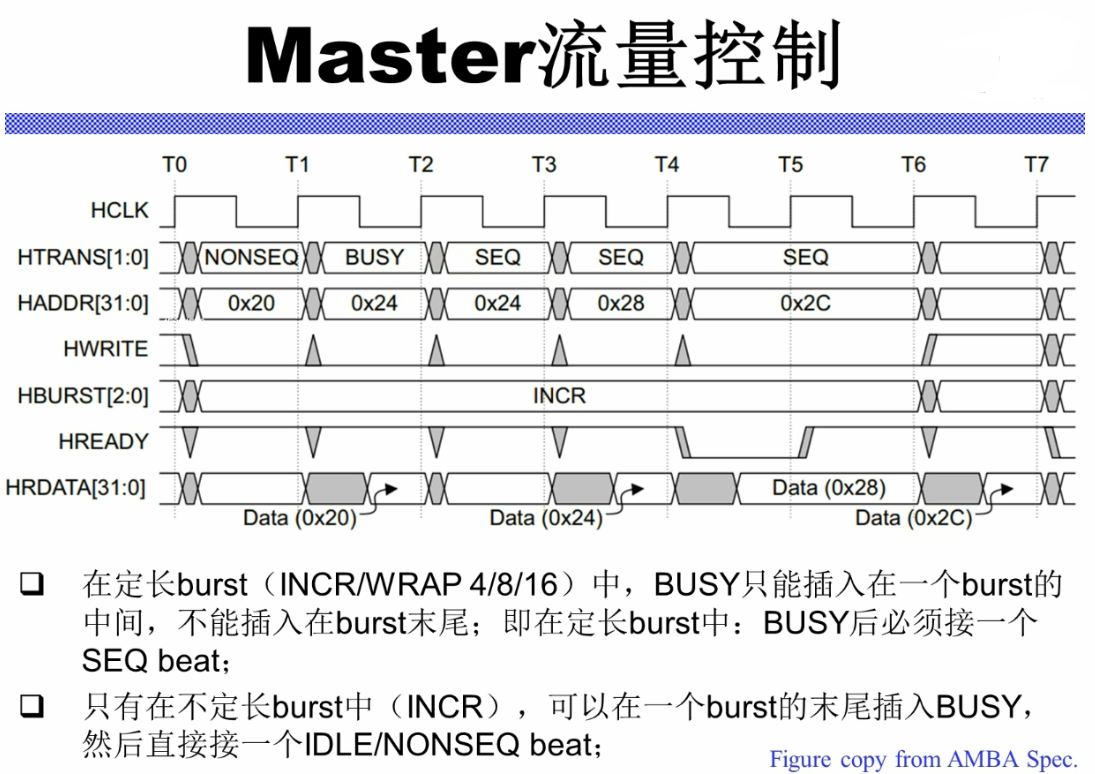

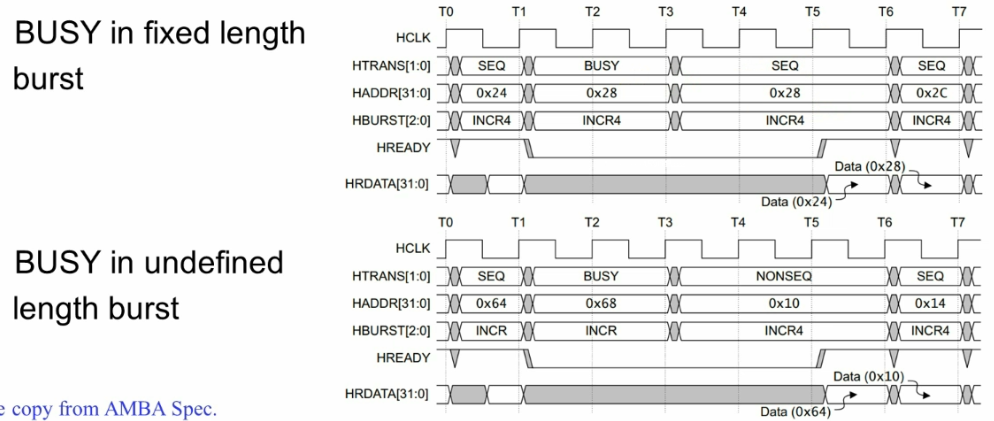

master靠驱动htrans=busy来插入wait cycle;

-

“一致原则”:在一个burst内除haddr/htrans外的其它addr phase的控制信号都应保持不变;

-

“尽早原则”: master在输出busy trans时,需要把其它addr phase的信号驱动到下一个beat的值;(master在插入busy的时候要把下一笔传输的addr放出来)

- “诚信原则”: master一但在addr phase发出一个nonseq/seq的transfer,通常需要等slave接收该addr phase的transfer cmd后才能改变addr phase的信号值发送下一个transfer cmd;

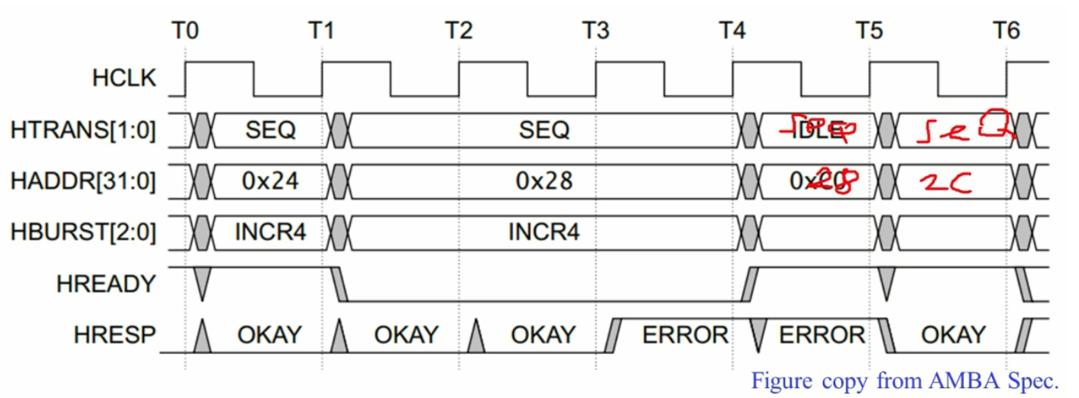

例外:在error response时,有特殊时序可以放弃一个己经发出的transfer cmd;

举例:

Master接收到ERROR response,有两种反应:- 无视ERROR response,继续这个burst传输

- 终止当前burst传输,在error响应时把htrans先改为idle; (这个要求在AMBA5中明确提出)

Master也可以无视ERROR response,继续这个burst传输:

-

“诚信原则”:如果master没有收到error response,master必须完成一个burst的所有beat传输;

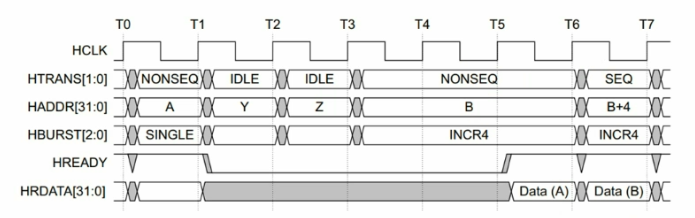

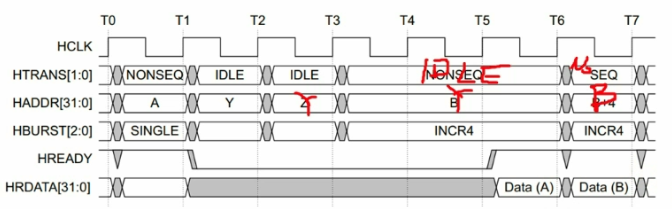

- “效率原则1”: master发出的idle trans,不管是否被slave接收,可以随时更换所有transfer cmd信息;

当slave拉低hready来扩展数据传输时,master若没有数据传输则drive IDLE状态,也可以随时由IDLE状态变为NONSEQ状态,这样做可以节省一个周期:

下图是加入没有这条规则的传输波形,每个IDLE状态都必须被Slave接受,那么IDLE状态将持续到hready=1的时钟上升沿。再后一个周期才能传输NONSEQ状态的传输。相对上图,后面的NONSEQ状态晚一周期。

-

“效率原则2” : master发出的busy trans,不管是否被slave接收,可以随时把htrans更换为seq(对于burst中间的busy)或nonseq/idle (对于不定长burst结束后的busy);

举例:同上面分析一样,如果没有这条原则,那么切换后的那一拍传输将相对慢一个时钟周期。

-

地址对齐

haddr需要对齐到hsize指定的byte边界,即:

8bit transfer,haddr可以从任意byte地址开始;

16bit transfer,haddr必须从2N byte地址开始;

32bit transfer,haddr必须从4N byte地址开始;

64bit transfer,haddr必须从8N byte地址开始; - 独占原则

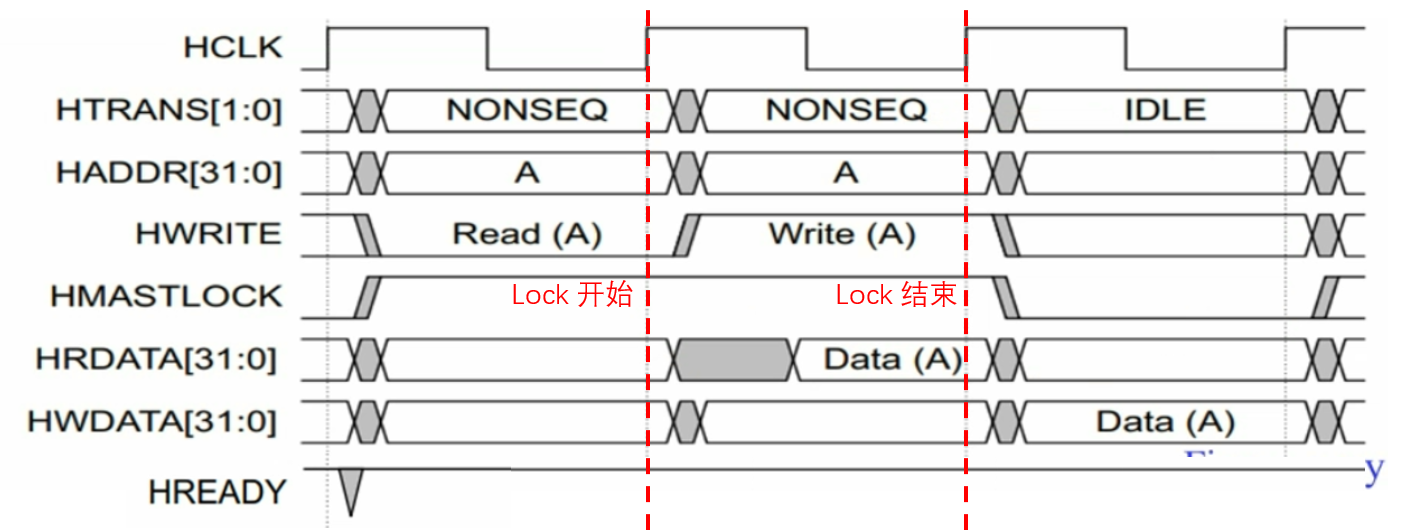

master发出locked transfer(hmasterlock=1)来保证一串AHB传输的独占性(atomic access) ; locked transfer一般是为了满足SW层面的“semaphore”操作需求,ARM CPU有对应的汇编指令:“SWP”;

在系统中,locked transfer是由bus结构保证的(非master/slave保证);在AMBA5中进一步明确:

- lock过程开始:

- master: hmasterlock=1 && hready =1;

- slave: hmasterlock=1 && hsel =1 && hready =1;lock过程结束:hmasterlock=O & hready = 1;

- 一个lock过程的头、中间、尾都可以插入IDLE trans;

- 在一个lock过程中,可以只有locked IDLE trans;

- 在一个lock过程中,所有的trans都只访问同一个slave;