1. PrimeTime基本概念

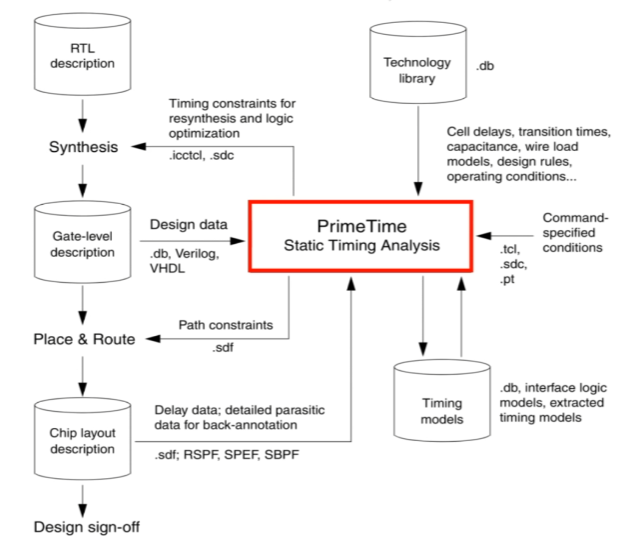

PrimeTime(PT)是Synopsys的sign-off quality的静态时序分析工具。PrimeTime可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,并提高时序收敛的速度。

PT在各阶段都有做,如下图。不过在逻辑综合和PR等阶段使用的延迟文件不一样,如sdc、sdf、spef文件等,区别在于延迟模型与精度不同,越到流程后面,模型越准确。

2. STA Concepts

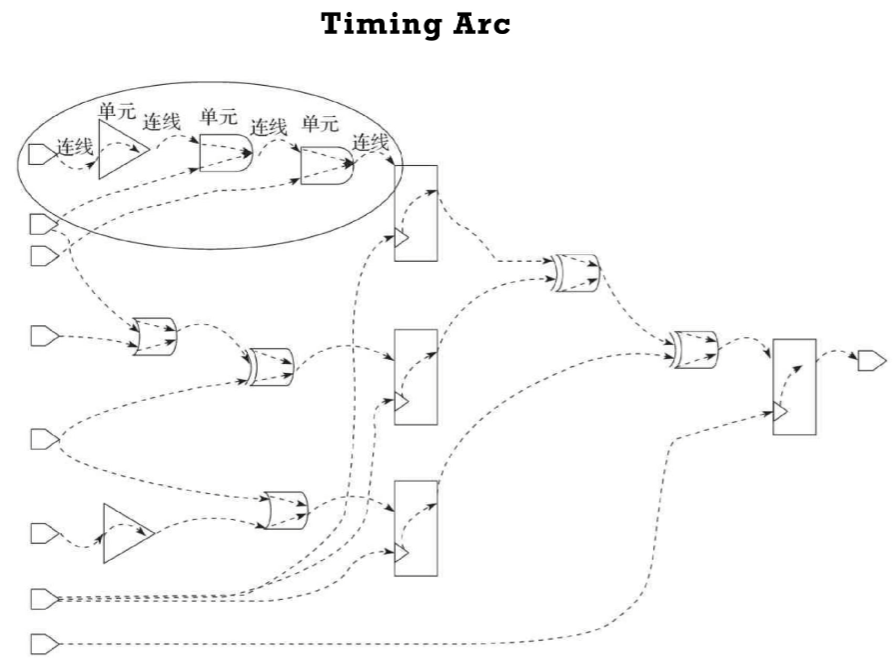

- 时序弧度

时序弧是用来描写描述两个节点延时信息的数据,通常分为:- 连线的延时:单元的输出端口和扇出网络负载之间的延时的信息。

- 单元的延时:单元的输入端口到单元的输出端口他们的延时信息。

一条完整的时序路径的信息是由这个连线的延迟,再加上这个单元的延迟这样来构成的。

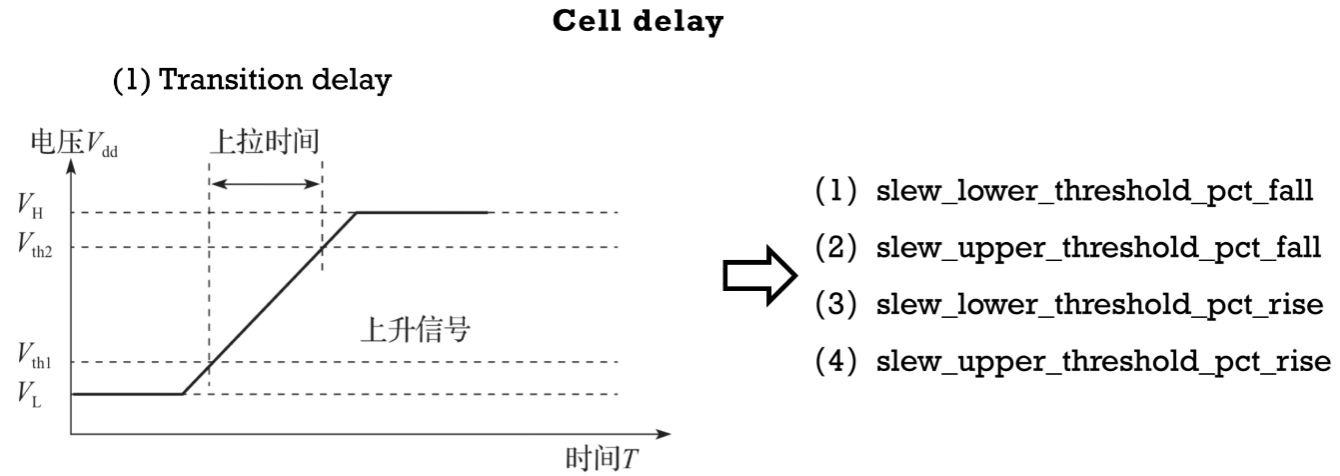

- 单元的延时(cell delay)

注意两个地方:- transition的延迟:数据翻转的延迟,关注两个时间点(百分之多少)卡在哪个位置。

- transition的延迟:数据翻转的延迟,关注两个时间点(百分之多少)卡在哪个位置。

- 逻辑的延迟:指的就是cell输入端口到输出端口的延迟。以这个反应器为例,如果是输入是高电平,输出是低电平,输入是低电瓶,那输出就是高电平。这样得到的延迟就是反向的一个延迟,存在两种延迟信息,从0到1或者从1到0这两种延迟信息,都是对应的cell delay。

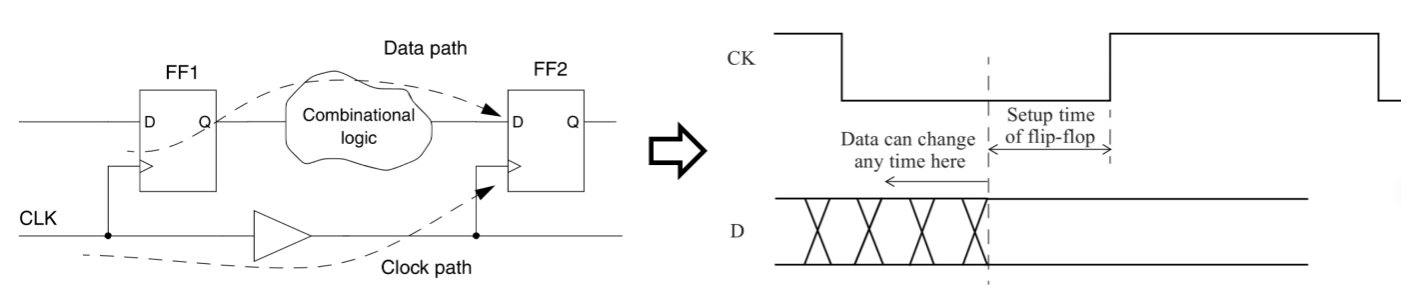

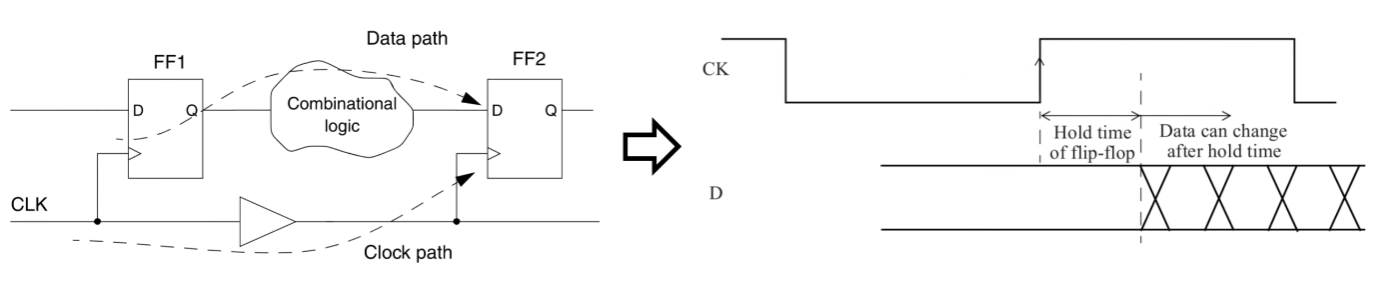

- 建立/保持时间(set up/hold time)

建立时间:时钟上升沿到来之前,数据必须要稳定下来的时间。如果能稳定下来,数据就能被D触发器上升沿稳定采样到,否则如果数据变化越过了建立时间,就会产生亚稳态。建立时间用来约束数据路径相对于时钟路径的最大延迟,不能越过建立时间。

保持时间:时钟上升沿之后,数据保持稳定的时间。如果数据在保持时间之内变化的,触发器依然得不到稳定的数据。保持时间用来约束数据路径相对于时钟路径的最小延迟(意思就是最小延迟必须越过保持时间,否则数据会落在保持时间内变化)。

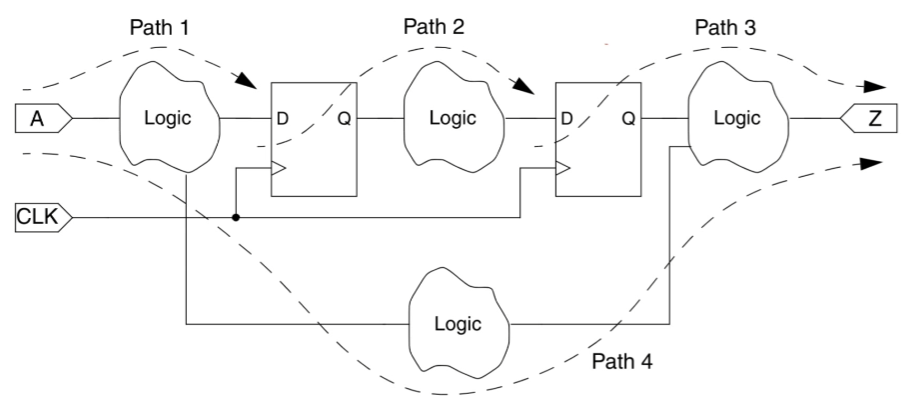

- 时序路径

进行静态时序分析的时候会把整个的电路会划分为不同的时序路径,然后再来检查每条时序路径上面的建立时间和保持时间是不是符合要求的约束。每个路径有一个起点和终点,时序路径的起点有两种:时序元件的clock pin或者设计的input port;时序路径的起点同样有两种:时序元件的data input pin或者设计的output port。 因此,时序路径共有4种: - clk→D

- clk→output port

- input port→D

- input port→output port

下图中总共有4条时序路径。 - 时钟域(clock domains)

通常SOC芯片中对时钟域的处理是全局异步,局部同步的方式,例如手机芯片中的大小核,每个核之间是异步时钟,每个核内是同一个时钟。而静态时序分析处理的是同步电路,无法处理异步电路。进行时序分析的时候,首先要根据时钟域来区分哪些是同步电路,哪些是异步电路,比如说在局部的同步电路种就可以用DC和PT来做综合或者做一些静态时序分析,对于跨时钟域的电路就要做一些约束来让PT知道,这些部分是没有办法去做静态实际分析。 - 操作条件

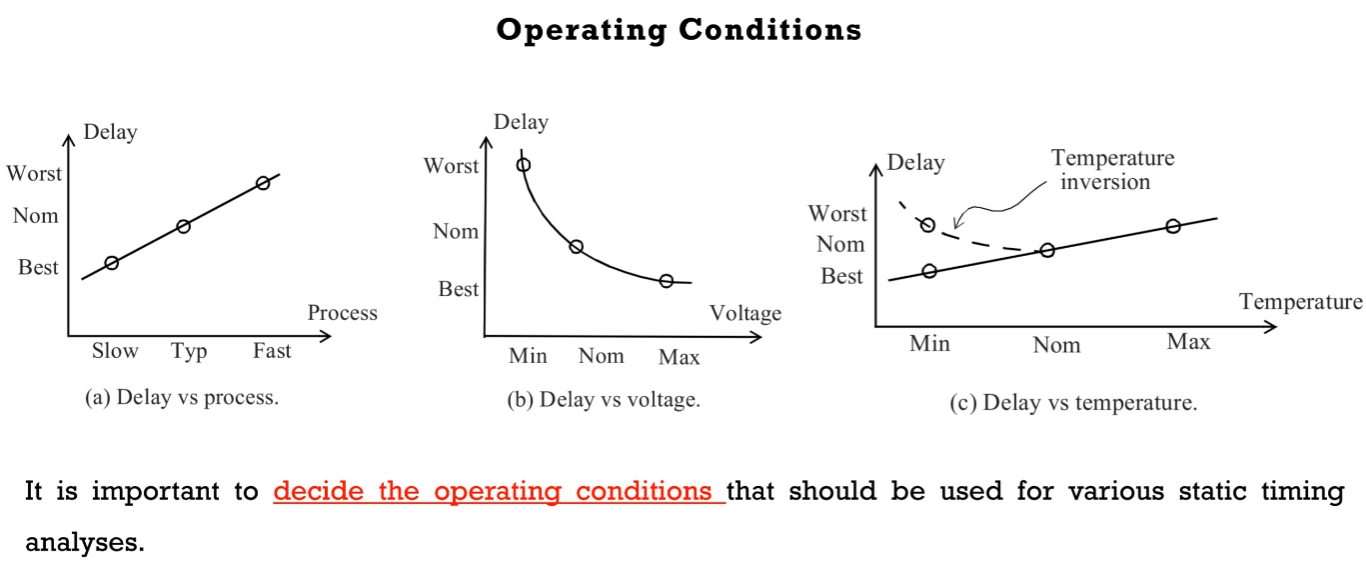

静态时序分析通常在特定操作条件下执行,操作条件定义为工艺制程(Process)、电压(Voltage)和温度(Temperature)的组合(PVT)。单元延迟和互连延迟需要指定操作条件计算。

半导体代工厂为数字设计提供三种制造工艺模型:slow工艺模型、typical工艺模型和fast工艺模型。slow和fast工艺模型代表代工厂制造工艺的极端情况。对于稳健设计,设计在制造工艺的极端情况以及温度和电源环境极端情况下进行验证。

下图是工艺制程(Process)、电压(Voltage)和温度(Temperature)分别于延迟的关系图:

注意!!!!!!!!!上图(a)子图中有错误,应该是反比。教材错了,那些搬运的没一个提出质疑呢(流汗.jpg)。具体可见[PVT (Process, Voltage, Temperature) – VLSI- Physical Design For Freshers]

从图中可以看出,制程越大延迟越大、电压越大延迟越小、温度越高延迟越大。通常来讲,高温加低电压这种极限的条件下,延迟最大(称为ss条件),此时来检查setup;低温加高电压这种极限的条件下,延迟最小(称为ff条件),此时来检查hold。

- WCS(Worst-Case Slow):工艺制程缓慢(制程越小),温度最高(比如 125°C),电压最低(比如标称 1.2V 减 10%)。

- TYP(Typical);典型工艺制程,典型温度(比如 25°C),典型电压(比如 1.2V)。

- BCF(Best-Case Fast):工艺制程快速(制程越大),温度最低(比如 -40°C),电压最高(比如标称 1.2V 加 10%)。

来自陕西