Verilog-HDL/SystemVerilog/Bluespec SystemVerilog插件是一款能够满足基本verilog代码编写需求的插件,其功能有代码高亮、代码片段补全、语法检查、ctags、模块自动例化等,可根据自己的功能需求按需配置。

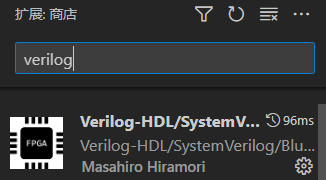

插件下载

先在vscode扩展程序中搜索下载插件:Verilog-HDL/SystemVerilog/Bluespec SystemVerilog

不同功能的实现可能需要安装另外的程序,接下来根据不同功能的实现,讲解各自的配置方法:

1. 代码高亮

安装Verilog-HDL插件即可,开箱即用,不需要额外配置,即可高亮verilog代码。

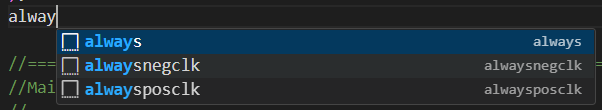

2. 代码片段补全

也是不需要额外的配置,输入代码,可以补全一些简单的代码片段:

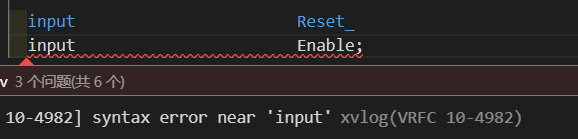

3. 语法检查

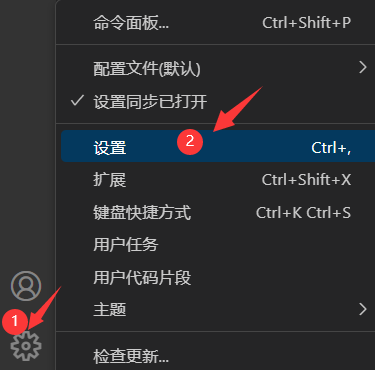

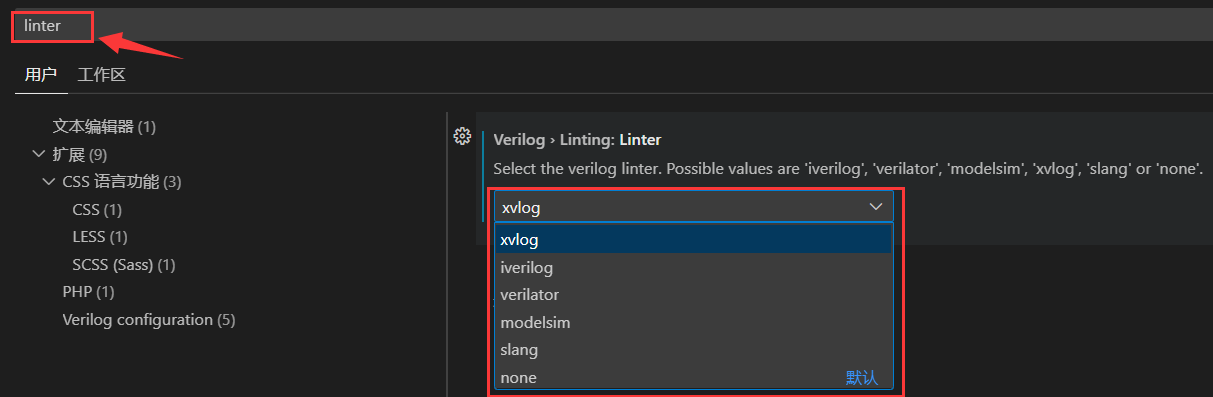

安装好Verilog-HDL插件后,在vscode设置中选择语法检查工具:

选择xvlog、iverilog、modelsim分别依赖vivado、modelsim、iverilog的语法检查工具。所以,该功能的实现需要先安装好对应的仿真器。我这里选用的是xvlog,调用的是vivodo的语法检查工具。

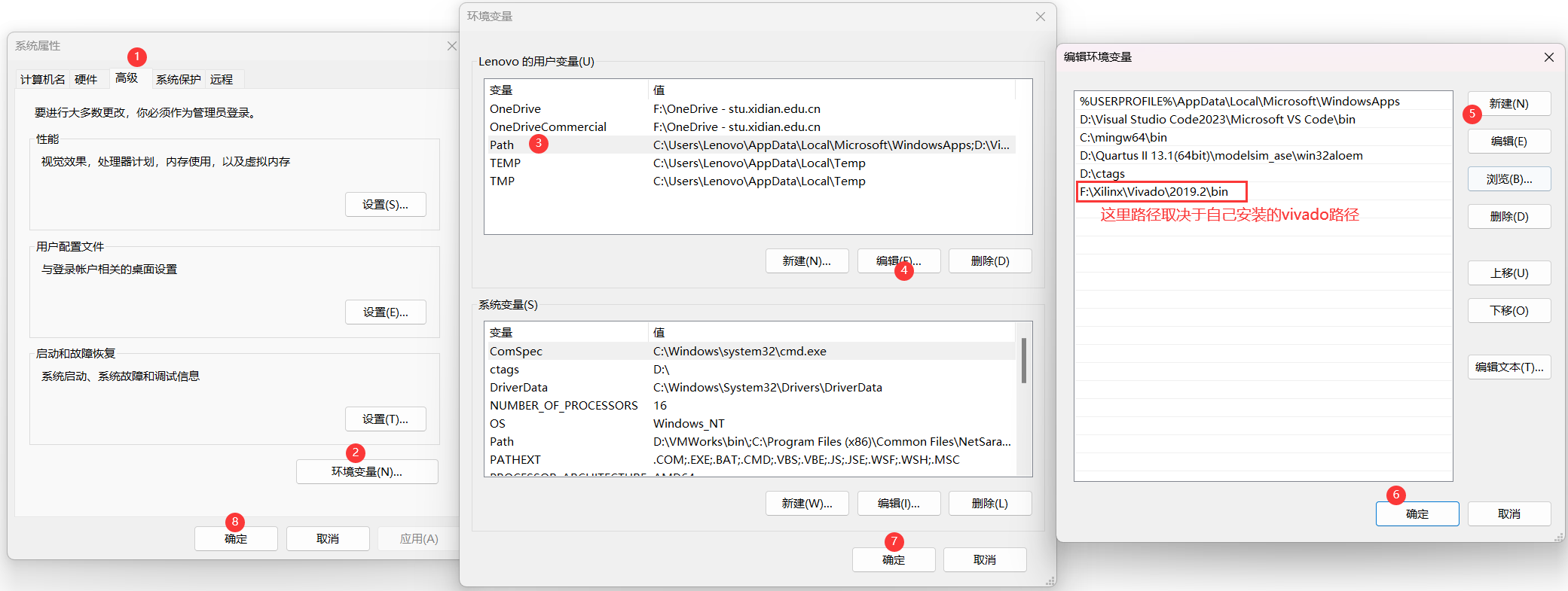

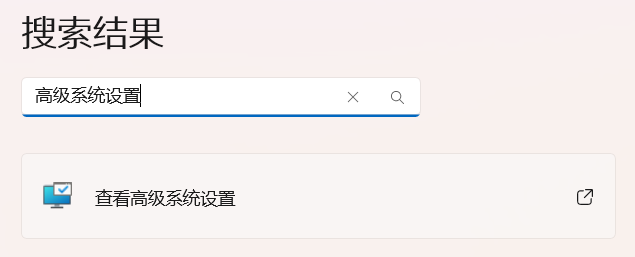

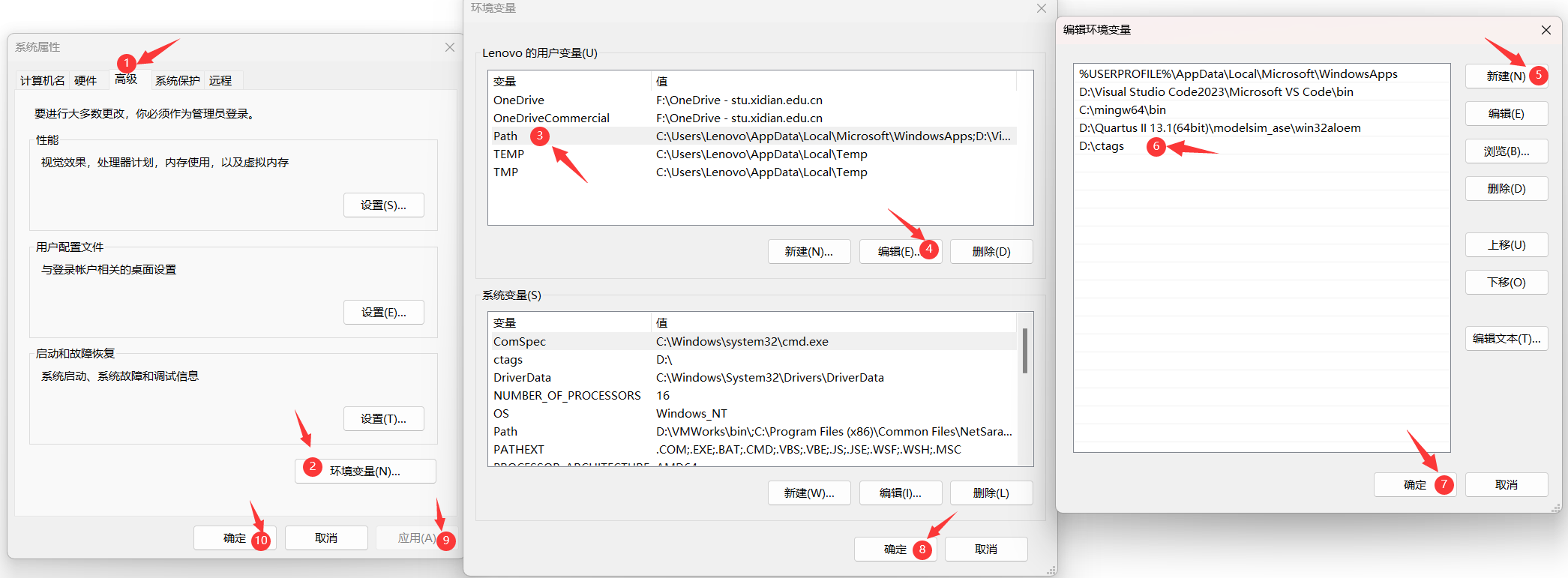

进行环境变量配置如下:

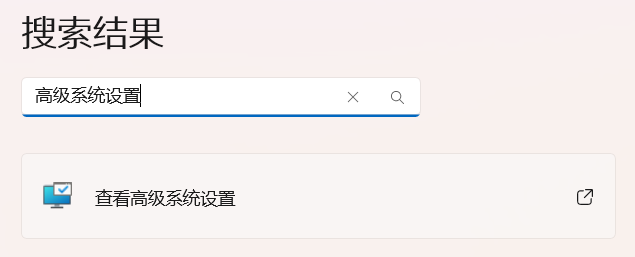

设置中搜索:高级系统设置→高级→环境变量:

将Vivado安装目录下面的bin文件夹加入到环境变量PATH里面:

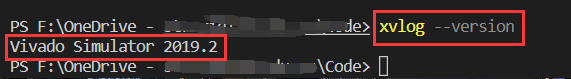

然后重启vscode,终端输入 xvlog --version显示正常版本信息则添加成功:

至此,vscode就可以检查语法错误了。

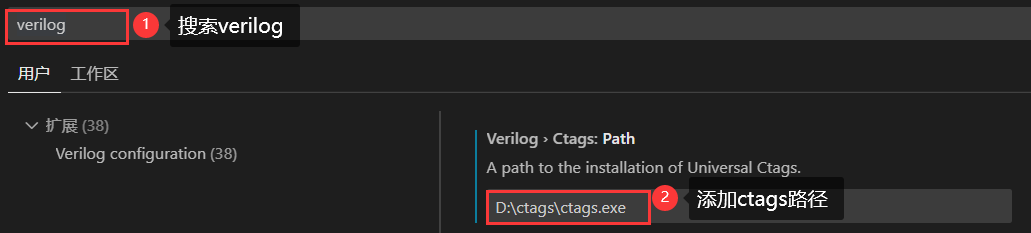

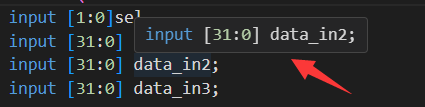

4. ctags

这个功能可以实现鼠标悬浮查看信号定义,跳转信号定义处。需要安装ctags,安装及配置教程如下:

- github下载ctags压缩包,解压到任意目录(记住目录,我这里目录是D:ctags)

- 将解压缩的目录添加至本地电脑环境变量

设置中搜索:高级系统设置→高级→环境变量:

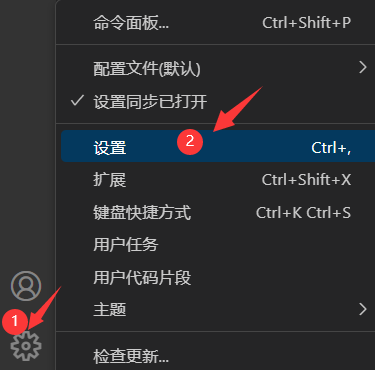

- vscode设置中设置Ctags路径,我这里是D:ctagsctags.exe

- 验证ctags是否安装成功

在vscode终端输入ctags –version,如下:

配置好之后,鼠标悬浮在信号上面可以查看信号定义,ctrl+鼠标左键点选信号可跳转至信号声明处。

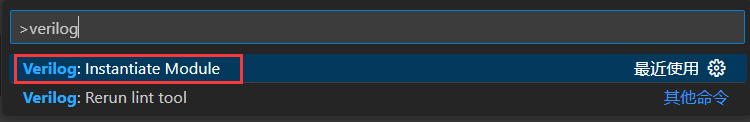

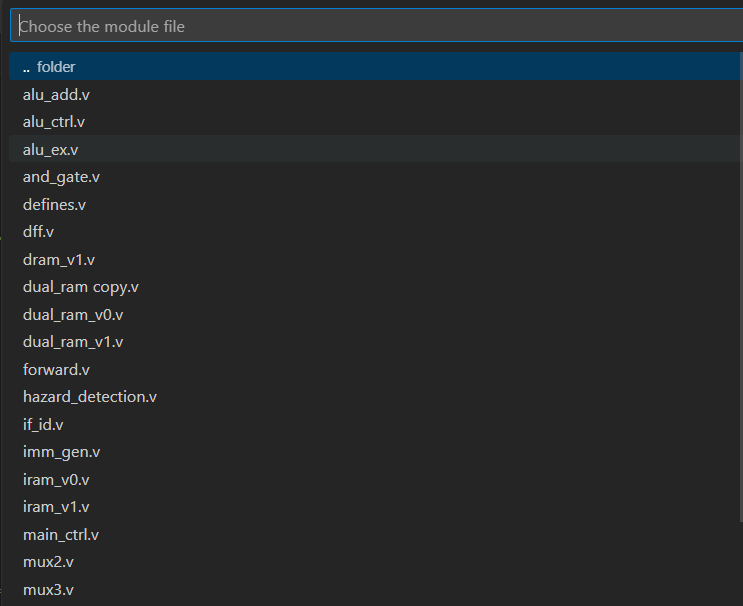

5. 模块自动例化

要实现这功能需要安装ctags,安装好之后,快捷键输入ctrl+shift+p打开命令面板,搜索命令:

选择需要自动例化的模块,回车即可

可参考教程:

vscode搭建Verilog HDL开发环境_vscode verilog插件_电路_fpga的博客-CSDN博客